### CONTENIDO

- 1. Introducción

- 2. Estructura, funcionamiento y simbología. Características I-V.

- 3. Lógica con nMOS

- 4. Lógica con pseudo-nMOS

- 5. Lógica con CMOS

- 6. El transistor MOS como interruptor

- 7. Lógica con puertas de paso

- 8. Puertas de transmisión

## **EL MOSFET**

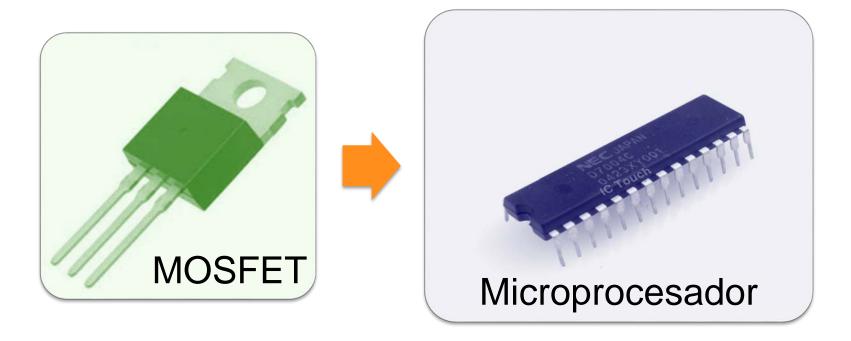

■ El transistor de efecto de campo metal-óxido-semiconductor o MOSFET (*Metal-oxide-semiconductor Field-effect transistor*) es el dispositivo más utilizado en la microelectrónica. La casi totalidad de los microprocesadores comerciales están basados en transistores MOSFET.

### IMPORTANCIA DEL TRANSISTOR MOSFET

- El MOSFET es el transistor más utilizado en circuitos digitales

- Es el artefacto más ampliamente fabricado a lo largo de la historia

- ■Se calcula que se han fabricado sextillones [10³6] de transistores

- Revolucionó la industria electrónica porque fue fundamental para la expansión de la microelectrónica a finales del siglo XX, llegando a ser el bloque fundamental de la electrónica digital en la era de la información.

- Actualmente, miles de millones de transistores MOS se encuentran dentro de un circuito integrado, como un chip de memoria o microprocesador

### HITOS PRINCIPALES

- 1959: Dawon Kahng y Martin Atalla en Bell Labs inventaron el primer MOSFET. Fueron galardonados con el Premio Nobel de Física

- ii. 1965: Fabricación, por parte de Digital Equipment Corp. (DEC), del PDP-8, un minicomputador que dominó el mercado

- iii. 1968: Intel desarrolló en tecnología MOS un conjunto de 12 chips que, en promedio, tenían unos 2000 transistores cada uno.

- iv. 1969: Se diseñó la primera generación de microprocesadores

- V. 1969: Kenneth Thompson y Dennis Ritchie de AT&T Bell Laboratories desarrollaron el SO UNIX

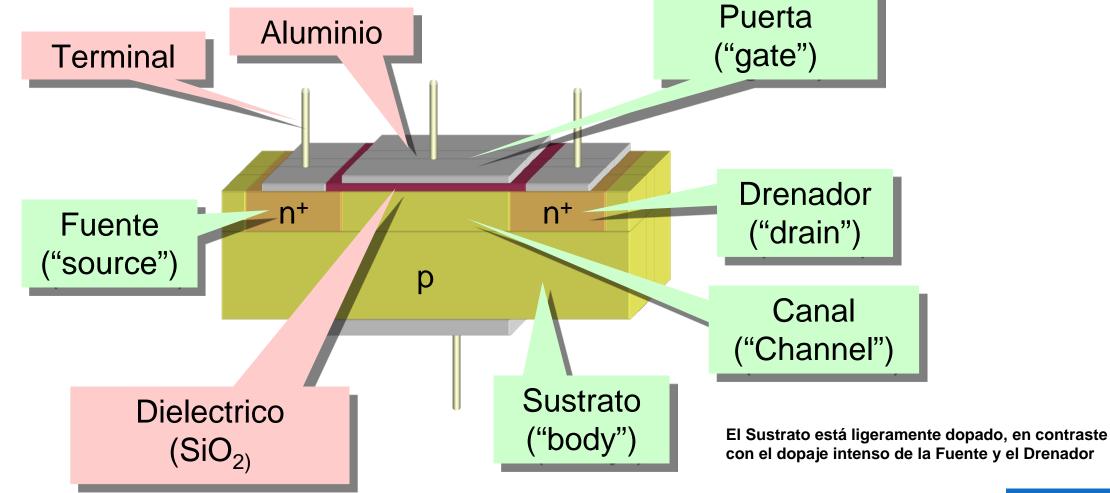

## **ESTRUCTURA**

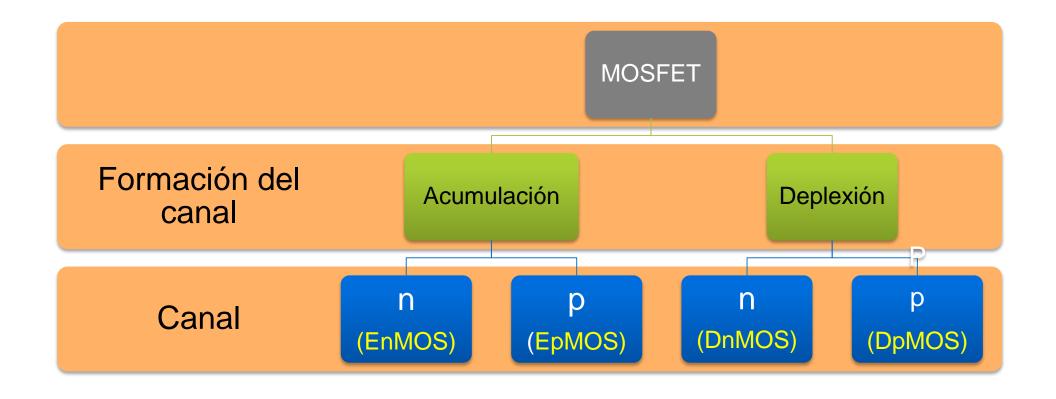

## TIPOS DE MOSFET

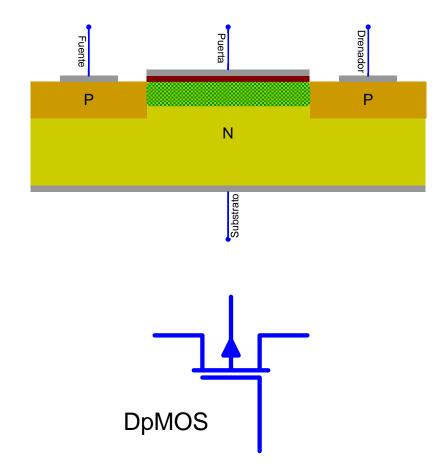

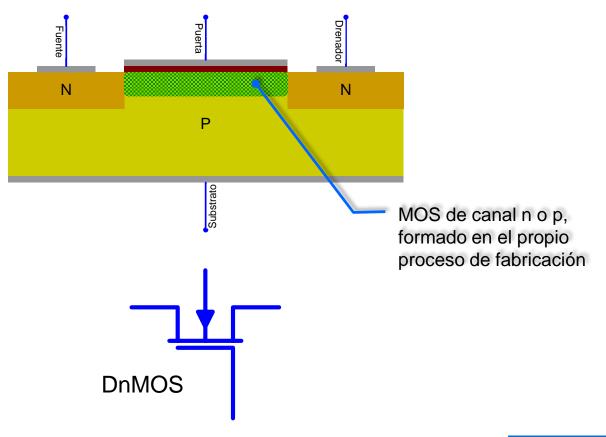

# MOSFET DE DEPLEXIÓN

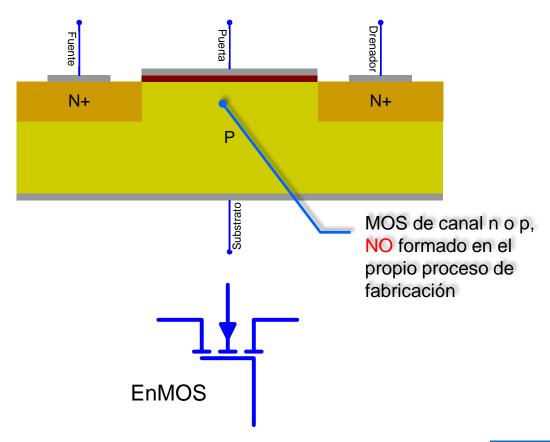

GEOMETRÍA Y SIMBOLOGÍA

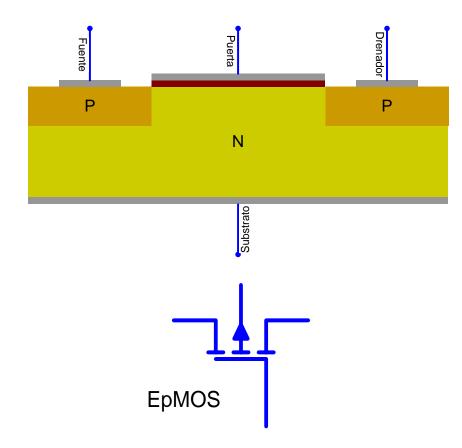

## MOSFET DE ACUMULACIÓN

GEOMETRÍA Y SIMBOLOGÍA

## FUNCIONAMIENTO DE UN ENMOS (1)

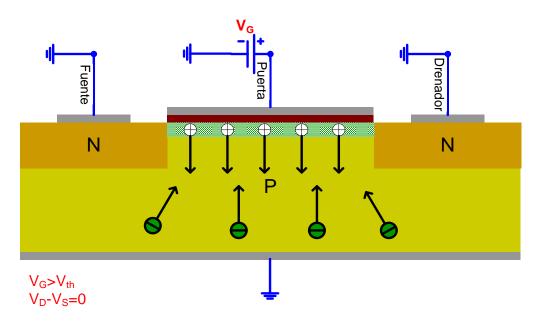

### Inducción de canal

El efecto de aplicar un voltaje en la puerta (G), da lugar a un campo eléctrico que repele a los huecos (cargas positivas mayoritarias) y atrae a los electrones libres (minoritarios) en el material P. Como consecuencia, se forma un canal N entre la fuente y el drenador en el que los mayoritarios son los electrones y los minoritarios los huecos. El fenómeno descrito (acumulación) no ocurre para cualquier tensión, sino solo cuando la tensión de puerta (VG) es mayor que un parámetro llamado voltaje de umbral (Vth).

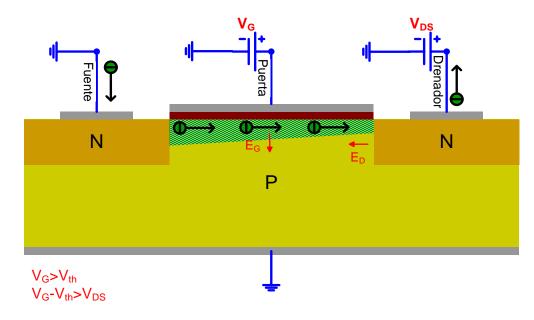

### **Funcionamiento lineal**

En este caso, si ,manteniendo el voltaje de puerta anterior, se aplica una tensión entre fuente y drenador, se fuerza una corriente eléctrica que atraviesa el canal (IDS). De tal forma que, con VDS>0, los electrones del canal se moverán hacia el contacto de drenador, tal como se indica en la figura. El valor de esta corriente dependerá del tamaño del canal y éste de la tensión VGS. Dicho de otra forma la  $I_{\rm DS}$  dependerá mas o menos linealmente de  $V_{\rm GS}$ .

Nótese que el canal de conducción se hace más angosto hacia el drenador debido a que la zona de carga espacial se hace mas gruesa ya que la unión PN está en inversa.

TC.Tema 4 Pg 11

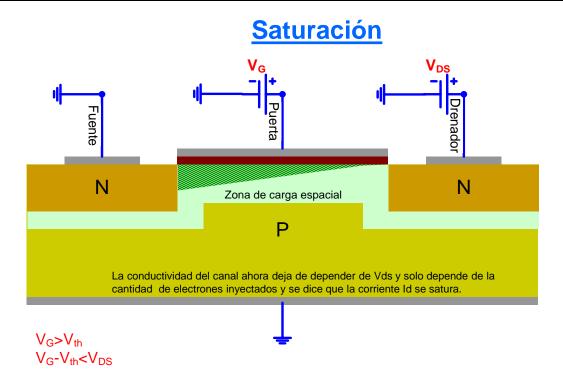

## FUNCIONAMIENTO DE UN ENMOS (Y 2)

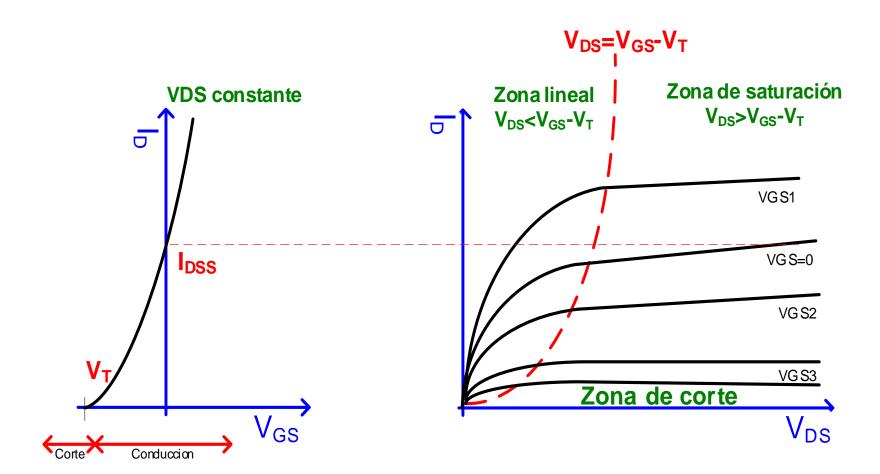

Cuando  $V_{DS}$ >  $V_{GS}$ - $V_{th}$  en algún punto intermedio del canal la zona de carga espacial estrangulará el canal, de tal forma que a partir de ese punto hacia el drenador ya no existirá canal formado. Al cerrarse el canal la corriente deja de depender de la magnitud del voltaje  $V_{DS}$  y se dice que la corriente  $I_{DS}$  se **satura**

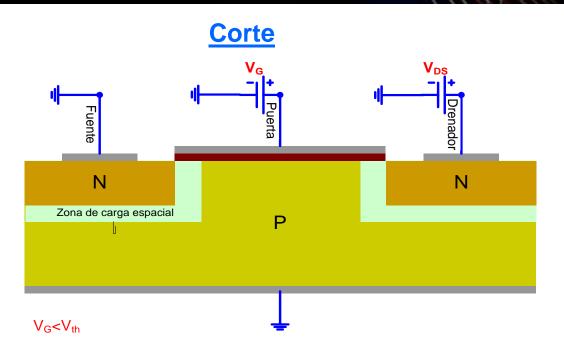

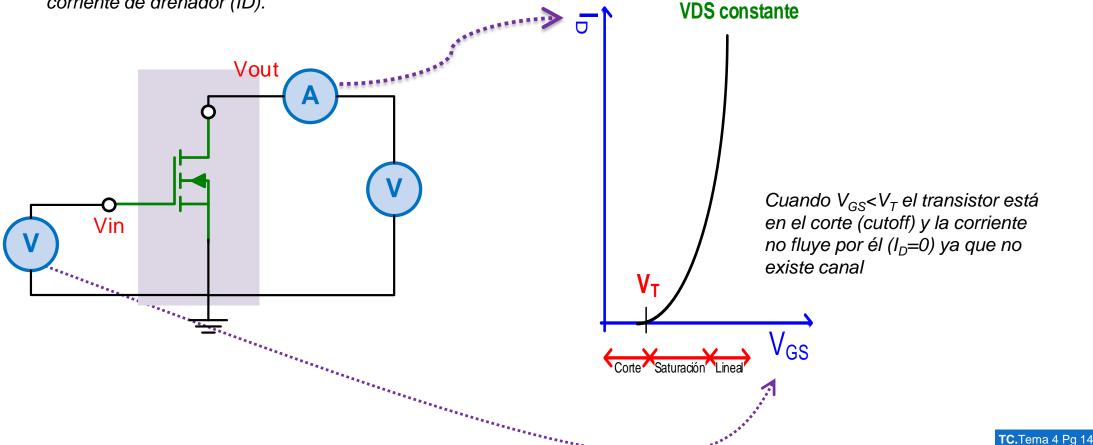

Cuando  $V_{GS}$ < $V_{th}$  la tensión de puerta no puede inducir el canal y la  $I_{DS}$  solo puede ser nula.

# **MOSFET**

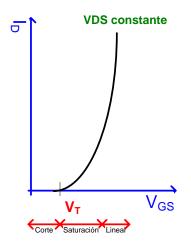

### **C**URVAS CARACTERÍSTICAS DE ENTRADA

V<sub>GS</sub>

# EnMOS

### **CURVAS CARACTERÍSTICAS DE ENTRADA**

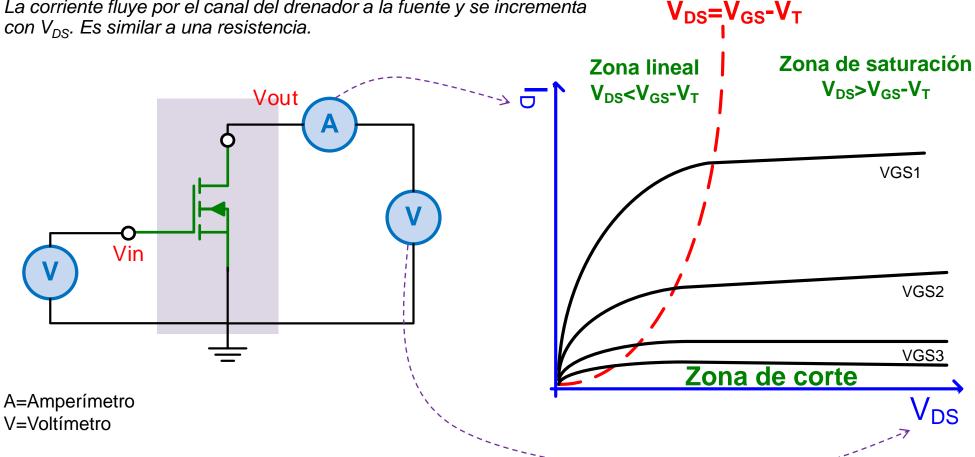

En la mayoría de las aplicaciones del MOSFET, la señal de entrada es la tensión de puerta (VG) y la señal de salida es la corriente de drenador (ID).

A=Amperimetro V=Voltimetro

### **ENMOS**

#### **CURVAS CARACTERÍSTICAS DE SALIDA**

$$V_{GS} > V_T$$

y  $V_{DS} < V_{GS} - V_T$

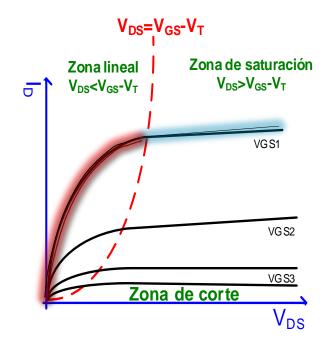

La corriente fluye por el canal del drenador a la fuente y se incrementa con V<sub>DS</sub>. Es similar a una resistencia.

Cuando el potencial efectivo de puerta es inferior al potencial entre el drenador y la fuente, o sea...

$$V_{DS} > V_{GS} - V_T$$

el transistor se encuentra en saturación. Como ya hemos visto anteriormente, en esta situación, el canal apenas alcanza el drenador y la corriente no aumenta proporcionalmente con la tensión de drenador ( $I_D$  = cte). El transistor se comporta como una fuente ideal de corriente.

# ENMOS ECUACIONES DE SALIDA

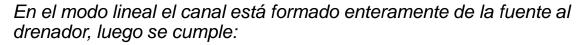

### Zona lineal

$$Vgs > Vt$$

;  $Vds < (Vgs - Vt)$

$$i_D = k \left[ (v_{GS} - V_t) v_{DS} - \frac{v_{DS}^2}{2} \right]$$

## Zona de saturación

$$Vgs > Vt$$

;  $Vds > (Vgs - Vt)$

$$i_D = \frac{k}{2} \left[ v_{GS} - V_t \right]^2$$

■ "k" es una constante igual a: k= KW/L. En donde <u>W</u> y <u>L</u> son la anchura y longitud del canal, respectivamente, y <u>K</u> es el llamado parámetro de transconductancia, específico de cada transistor.

■V<sub>t</sub> es la tensión umbral

Zona de Corte Ig = 0 ; VGS < Vt ID = 0

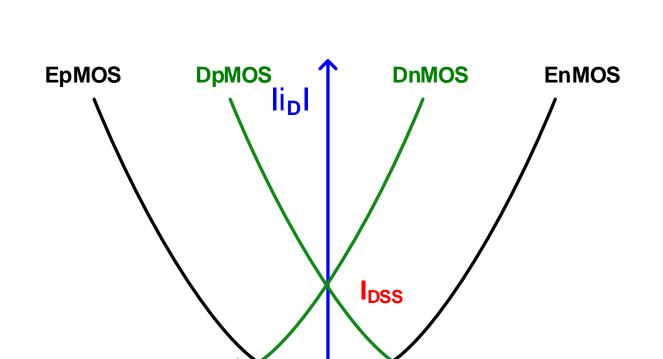

# **DNMOS**CURVAS CARACTERÍSTICAS

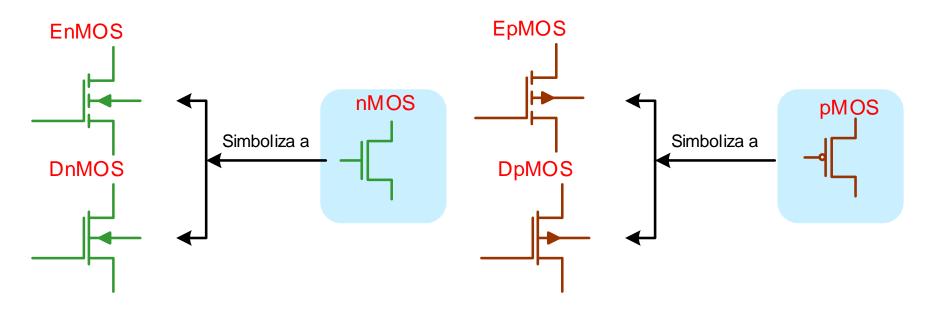

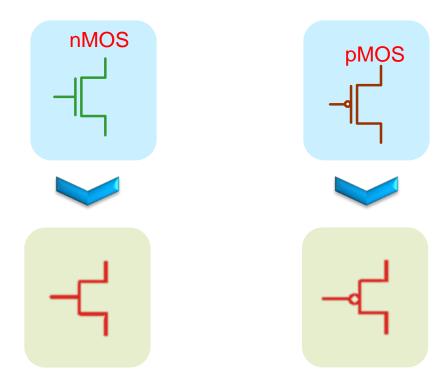

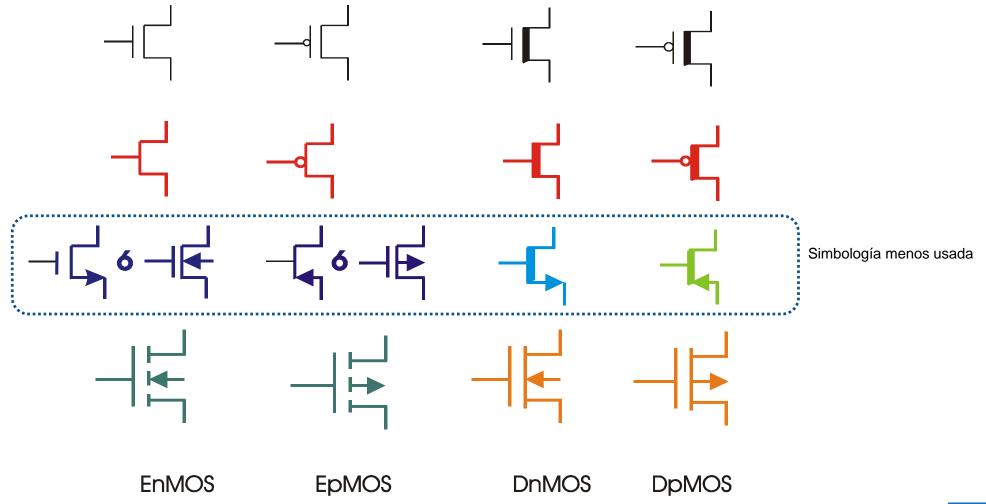

## SIMBOLOGÍA SIMPLIFICADA (1)

- Hasta ahora los símbolos esquemáticos MOSFET utilizados muestran el drenador (D), la puerta (G), la fuente (S) y el substrato que está sin conectar.

- En los símbolos simplificados propuestos no se indica la conexión del sustrato.

- Además, las puertas de los dispositivos de canal p y n difieren.

- El dispositivo de canal p se identifica por una "burbuja" en la entrada de la puerta. En cambio, el dispositivo de canal n no tiene la "burbuja". La presencia o ausencia de una "burbuja" en la entrada de la puerta se utiliza para significar el nivel lógico que hace conducir al transistor (ON).

# SIMBOLOGÍA SIMPLIFICADA (2)

Notación moderna mas simplificada

# SIMBOLOGÍA SIMPLIFICADA (Y 3) RESUMEN Y OTROS SÍMBOLOS

# **M**ODOS DE FUNCIONAMIENTO

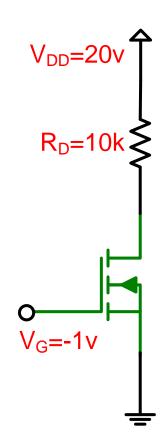

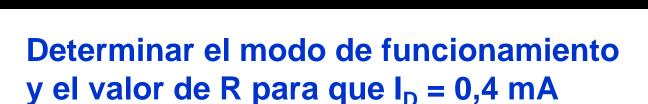

EJEMPLO 1

# Determinar el modo de funcionamiento del transistor en el circuito de la figura

El símbolo nos indica que es un nMOS de acumulación, como  $V_G > V_T$ , está en conducción (ver la gráfica de entrada).

Si lo suponemos saturado, tendría que cumplirse:

$$I_D = \frac{K}{2} [V_{GS} - V_T]^2 \quad \Box \quad I_D = 4 \, mA$$

Con este resultado analizamos la malla de salida y obtenemos:

$$V_{DD} = V_{DS} + I_D R$$

$\Rightarrow$  20 =  $V_{DS} + 40$   $V_{DS} = -20v$

$$V_{DS} = -20v$$

### **Datos**

$$V_t = -3V$$

$$\frac{K}{2} = 1mA/V^2$$

Como no se cumple que V<sub>DS</sub>>V<sub>GS</sub>-V<sub>T</sub> el transistor está en la **zona lineal**

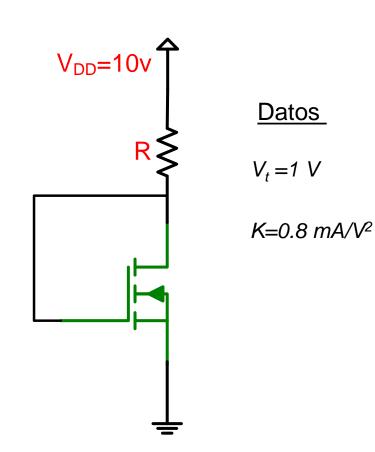

### **M**ODOS DE FUNCIONAMIENTO

#### EJEMPLO 2

Por la manera en que está conectado EnMOS  $V_{DS} = V_{GS}$

Por lo tanto, se cumple que  $V_{DS} > V_{GS} - V_t$  y el transistor opera en saturación.

La ecuación que describe su comportamiento en saturación es:

$$I_D = \frac{K}{2} [V_{GS} - V_T]^2$$

$1 = [V_{GS} - 1]^2$   $V_{GS} = 2V$   $V_{GS} = 0V$

La segunda solución no es viable pues V<sub>GS</sub>>Vt

$$V_{DD} = V_{DS} + I_D R$$

$\Rightarrow$  10=  $V_{DS} + 0.4 \cdot R$   $\Rightarrow$   $R = 20k$

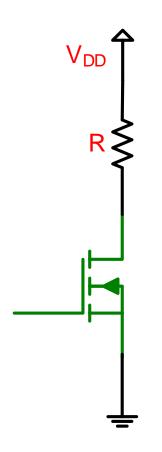

## RECTA DE CARGA Y PUNTO DE FUNCIONAMIENTO DE OPERACIÓN

# LÓGICA CON nMOS

- 1. El inversor

- 2. El MOS como resistencia de pull-up

- 3. La puerta NOR

- 4. La puerta NAND

- 5. La lógica psudo-nMOS

- El primer tipo de inversor MOS que se construyó fue muy similar al inversor construido con transistores bipolares

- ■Esto es, una estructura simple que conecta una resistencia en serie de *pull-up* con el drenador de un transistor MOS

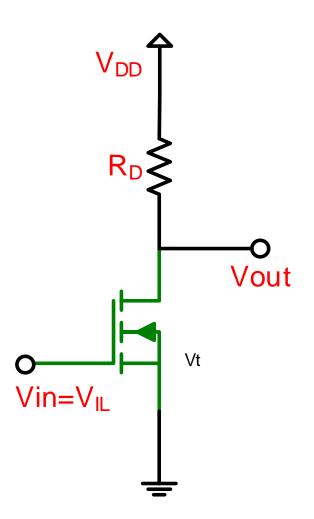

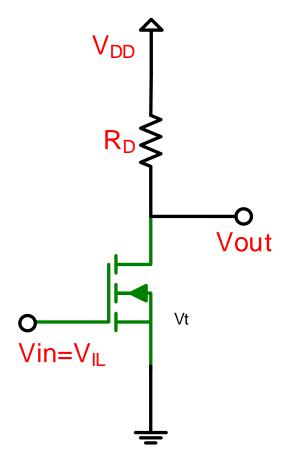

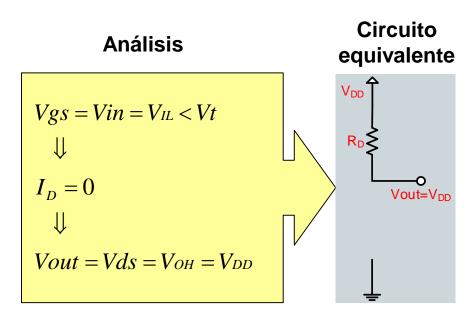

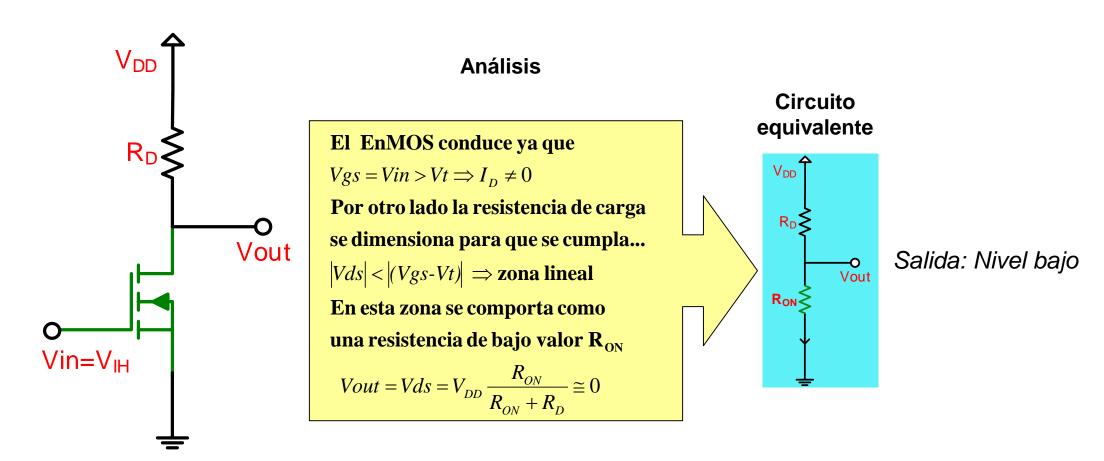

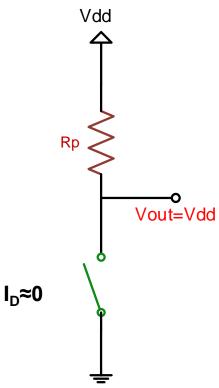

### ANÁLISIS DEL INVERSOR nMOS: CORTE

Salida: Nivel alto (V<sub>DD</sub>)

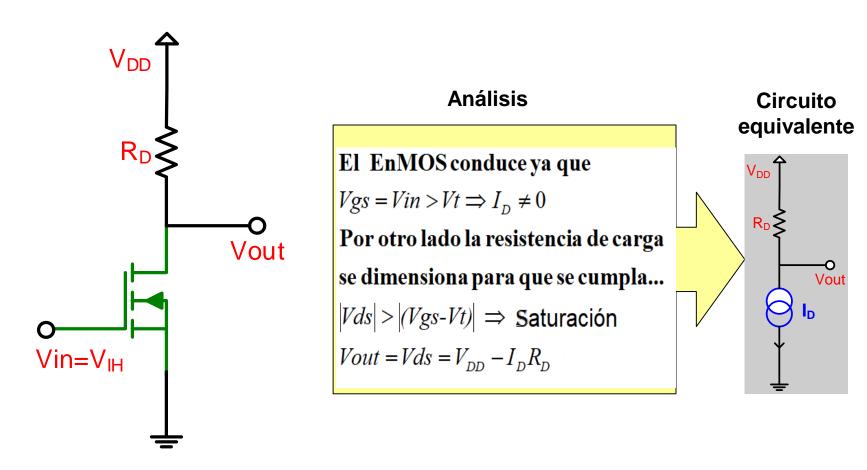

### ANÁLISIS DEL INVERSOR nMOS: SATURACIÓN

Entrada: Nivel alto (IH)

### ANÁLISIS DEL INVERSOR nMOS: ZONA LINEAL

Entrada: Nivel alto (IH)

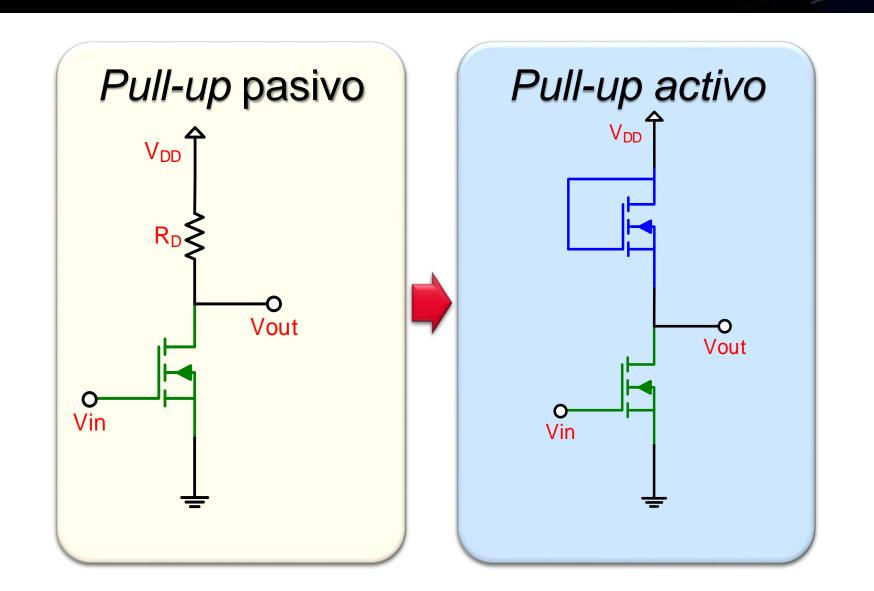

## EL MOS COMO RESISTENCIA DE PULL-UP

- En contraste con la tecnología bipolar, las resistencias raras veces son usadas como el elemento de pull-up en un inversor, debido a que ocupan un área 10 veces, o más, superior a un transistor y su implementación es cara.

- Por ello, se usan los transistores de deplexión y acumulación en lugar de resistencias que aportan beneficios como la simplificación del proceso de fabricación y mayor corriente

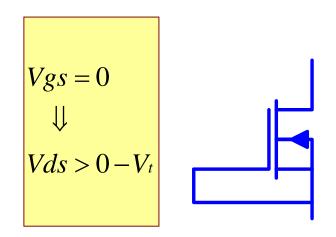

En la figura, se puede apreciar que Vgs=0, por tanto se cumplirá la condición de saturación: Vds > Vgs-Vth

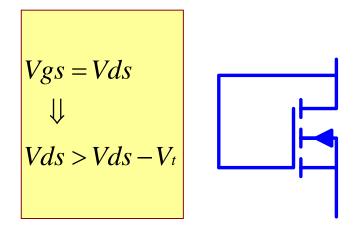

En la figura, se puede apreciar que Vgs=Vds, por tanto se cumplirá la condición de saturación: Vds > Vgs-Vth

## EVOLUCIÓN DEL INVERSOR NMOS

# PUERTA NOR nMOS

# PUERTA NAND nMOS

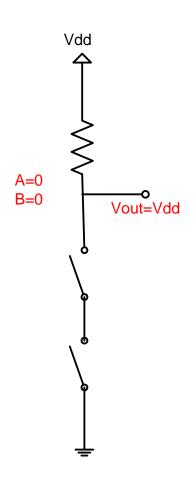

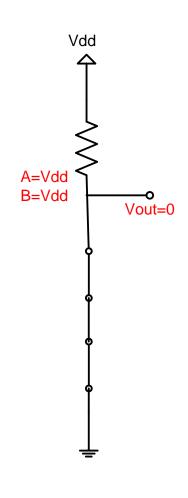

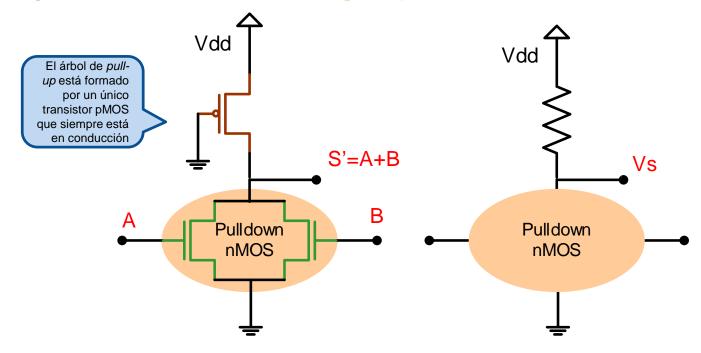

## LÓGICA PSEUDO-nMOS

- Como ya hemos visto en las anteriores dispositivas, se pueden construir puertas lógicas usando transistores nMOS y resistencias de pull-up, que pueden hacerse con transistores MOS deplexión (conducen cuando Vgs=0).

- ■Esta lógica recibe el nombre de lógica pseudo-nMOS.

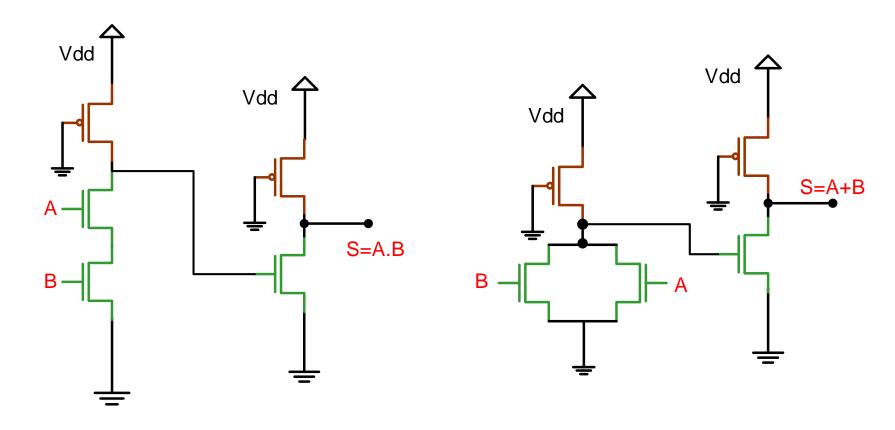

## **LÓGICA PSEUDO-NMOS** PUERTA AND Y OR

Añadiendo un inversor a la puerta NAND se puede conseguir una implementación AND con nMOS o también una OR

# LÓGICA PSUDO-nMOS

DISEÑO COMPLEJO

# LÓGICA CON CMOS

- 1. Introducción

- 2. El inversor

- 3. El MOS como resistencia de pull-up

- 4. La puerta NOR

- 5. La puerta NAND

- 6. La lógica psudo-nMOS

## INTRODUCCIÓN

- La tecnología CMOS (complementary metal-oxide-semiconductor) es una de las mas empleadas en la fabricación de circuitos integrados.

- ■Fué desarrollada por Wanlass y Sah, de Fairchild Semiconductor, a principios de los años 60

- Su principal característica consiste en la utilización conjunta de transistores de tipo pMOS y tipo nMOS

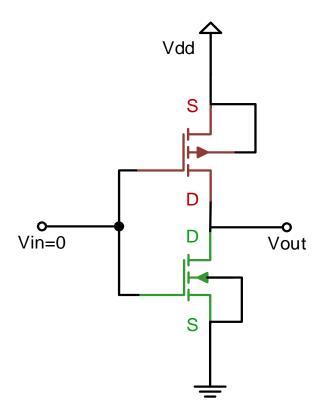

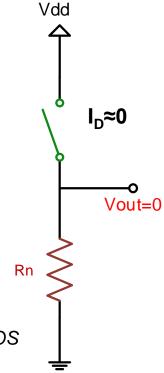

### **EL INVERSOR CMOS**

- Un circuito inversor CMOS se compone de dos MOSFETs. La parte superior es un transistor de tipo EpMOS; mientras que el transistor inferior es un tipo EnMOS. Los sustratos están conectados respectivamente a la alimentación y la masa. Ambas puertas (g) están conectadas a la línea de entrada. La línea de salida se conecta a los drenadores de ambos MOSFETs.

- Los dos MOSFETS deben estar perfectamente emparejados para un funcionamiento óptimo, es decir, deben tener el mismo parámetro de tensión umbral (V<sub>T</sub>).

## **EL INVERSOR CMOS**

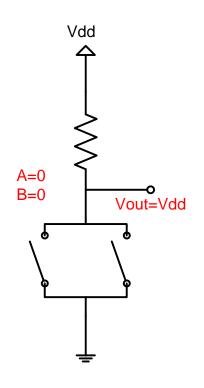

### **A**NÁLISIS ESTÁTICO: NIVEL BAJO

#### **Análisis**

$$V_{in} = V_{GSn} = 0 < V_t$$

$V_{GSp} = -V_{dd}$

$\downarrow$

$nMOS: cortado$

$pMOS: conduce(lineal)$

$\downarrow$

$Vout = V_{DD}$

# Circuito equivalente

Cuando Vin es bajo (0 V),los transistores nMOS y pMOS están OFF y ON (lineal) respectivamente, estableciéndose un camino entre VDD y Vout, a través de una pequeña resistencia Rn, dando lugar a un nivel alto de salida.

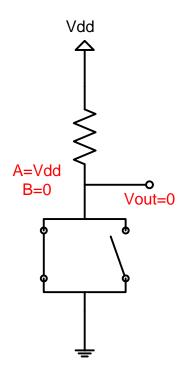

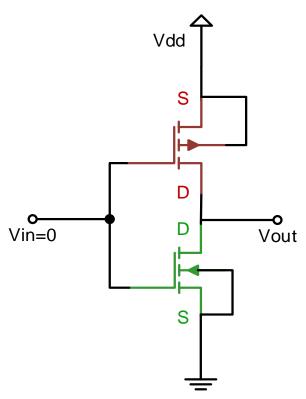

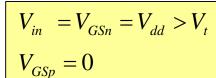

## EL INVERSOR CMOS

#### **ANÁLISIS ESTÁTICO: NIVEL ALTO**

Vdd

D

Vout

#### **Análisis**

*nMOS* : *conduce*(*lineal*)

pMOS : cortado

Vout = 0

Circuito equivalente

Cuando Vin es una tension alta e igual a Vdd, el transistor EnMOS está ON, mientras que el EpMOS está OFF. Esto conduce al circuito equivalente de la figura, en la que se aprecia un camino directo entre Vout y la masa; resultando un valor de salida de 0v.

Finalmente, nótese que tanto en este caso como en el anterior no hay consumo de potencia

Vin=Vdd

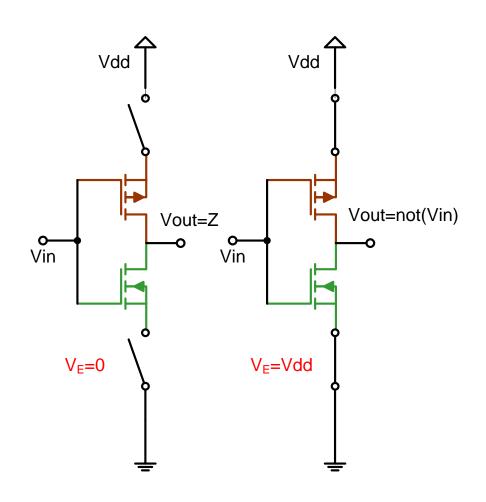

# EL INVERSOR CMOS CON SALIDA TRIESTADO

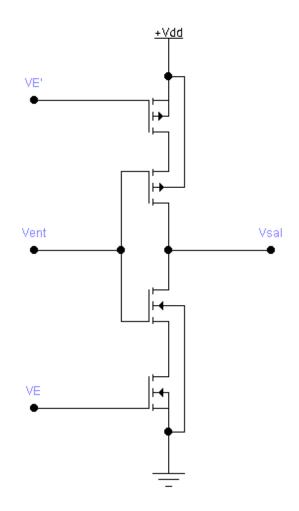

## ESTRUCTURA DE LOS CIRCUITOS LÓGICOS CMOS

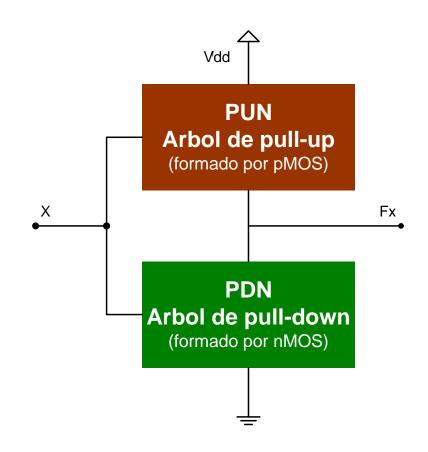

- Todo circuito combinacional CMOS estático se basa en la conexión de dos árboles duales con entradas comunes (x) y salida común (Fx), que en estado estacionario no conducen simultáneamente

- Arbol de pull-up, formado únicamente por transistores pMOS, que conectan condicionalmente (en función de las entradas) la salida a Vdd.

- Arbol de de pull-down, formado únicamente por transistores nMOS, que conectan condicionalmente (en función de las entradas) la salida a Vss.

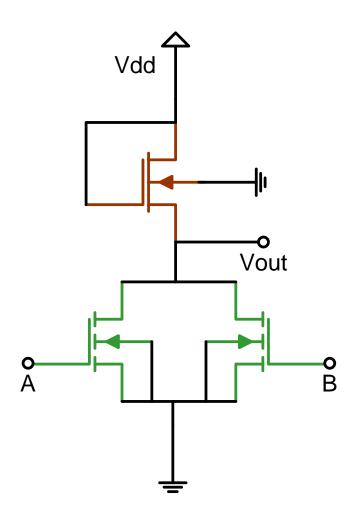

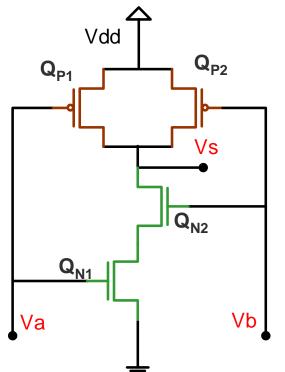

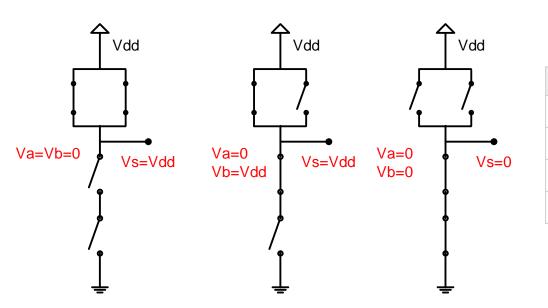

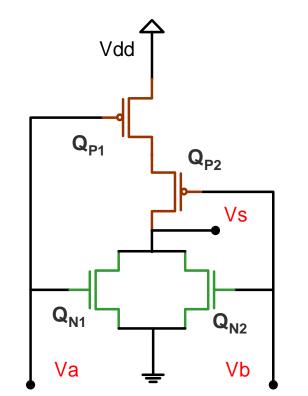

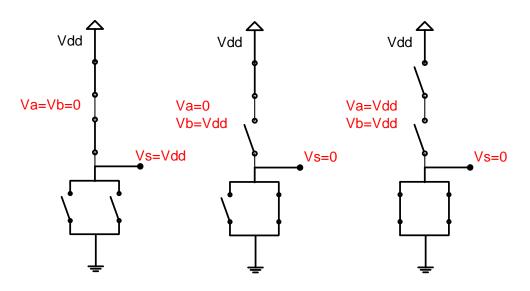

## LA PUERTA NAND CMOS

#### Circuitos equivalentes según las entradas

| Α | В | Q <sub>P1</sub> | $Q_{P2}$ | $Q_{N1}$ | $Q_{N2}$ | S |

|---|---|-----------------|----------|----------|----------|---|

| 0 | 0 | ON              | ON       | OFF      | OFF      | 1 |

| 0 | 1 | ON              | OFF      | OFF      | ON       | 1 |

| 1 | 0 | OFF             | ON       | ON       | OFF      | 1 |

| 1 | 1 | OFF             | OFF      | ON       | ON       | 0 |

En una puerta NAND CMOS, las entradas en nivel alto, hacen que los transistores  $Q_{P1}$  y  $Q_{P2}$  entren en corte y ambos transistores  $Q_{N1}$  y  $Q_{N2}$  en conducción (Ver Tabla). La salida pasa a bajo (0) a través de  $Q_{N1}$  y  $Q_{N2}$ .

Cuando ambas entradas están en bajo,  $Q_{P1}$  y  $Q_{P2}$  entran a conducción y  $Q_{N1}$  y  $Q_{N2}$  entran a corte. La salida pasa a alto (1) a través de  $Q_{P1}$  y  $Q_{P2}$ .

TC.Tema 4 Pg 44

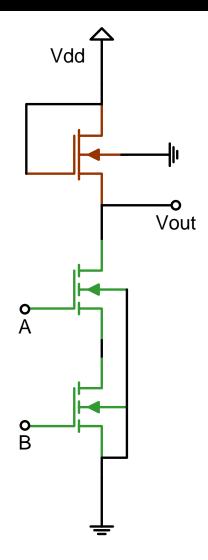

## LA PUERTA NOR CMOS

#### **A**NÁLISIS ESTÁTICO

### Circuitos equivalentes según las entradas

| Α | В | Q <sub>P1</sub> | $Q_{P2}$ | Q <sub>N1</sub> | Q <sub>N2</sub> | S |

|---|---|-----------------|----------|-----------------|-----------------|---|

| 0 | 0 | ON              | ON       | OFF             | OFF             | 1 |

| 0 | 1 | ON              | OFF      | OFF             | ON              | 0 |

| 1 | 0 | OFF             | ON       | ON              | OFF             | 0 |

| 1 | 1 | OFF             | OFF      | ON              | ON              | 0 |

En una puerta NOR CMOS, las entradas en nivel alto, hacen que los transistores  $Q_{P1}$  y  $Q_{P2}$  entren en corte y ambos transistores  $Q_{N1}$  y  $Q_{N2}$  en conducción (Ver Tabla). La salida pasa a bajo (0) a través de  $Q_{N1}$  y  $Q_{N2}$ .

Cuando ambas entradas están en bajo,  $Q_{P1}$  y  $Q_{P2}$  entran a conducción y  $Q_{N1}$  y  $Q_{N2}$  entran a corte. La salida pasa a alto (1) a través de  $Q_{P1}$  y  $Q_{P2}$ .

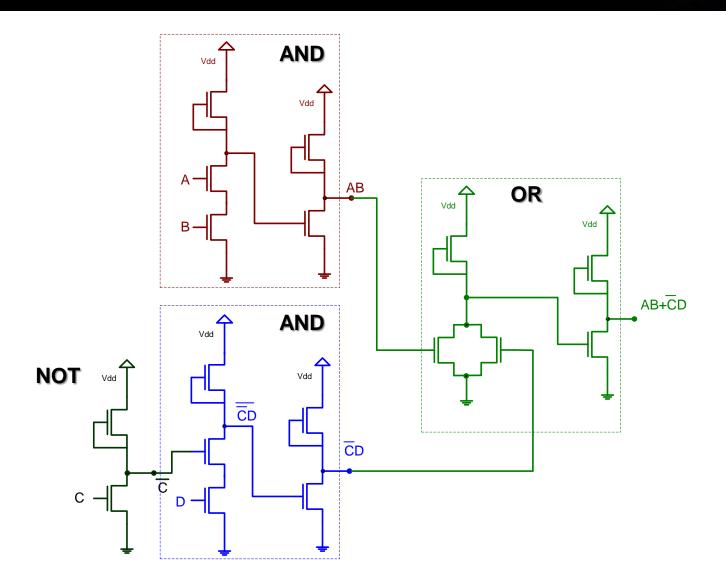

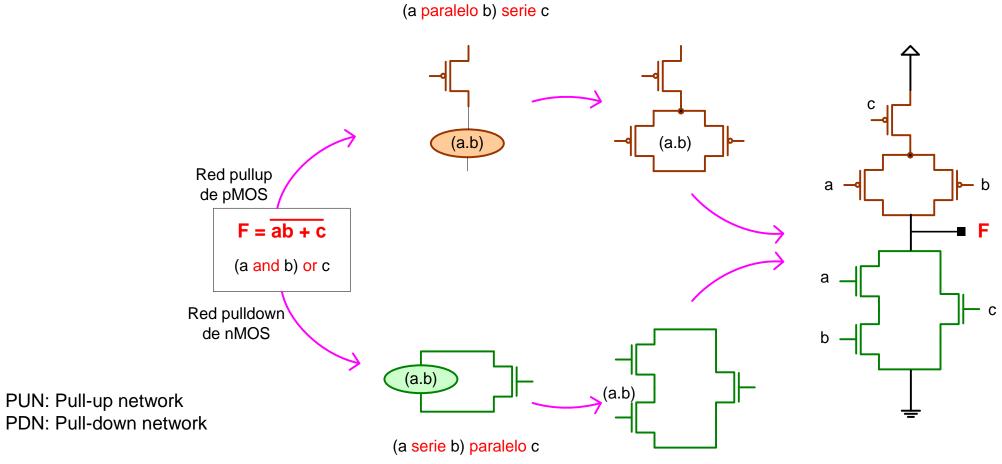

# LÓGICA CMOS DISEÑO COMPLEJO (I)

Como se puede ver en la implementación de F, esta se divide en dos caminos: la implementación del PUN y PDN. Estas dos redes son duales.

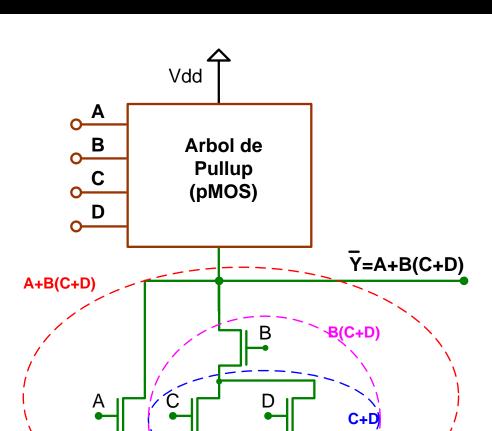

## LÓGICA CMOS

DISEÑO COMPLEJO (II): IMPLEMENTACIÓN DE LA FUNCIÓN A+B(C+D)

Como se puede ver en la figura, la pulldown network (y también la PUN, aunque dual) se reduce a estructuras serie o paralelo jerarquizadas

# EL TRANSISTOR MOS COMO INTERRUPTOR

- 1. El interruptor ideal

- 2. Modelo de interruptor nMOS

- 3. Modelo de interruptor pMO

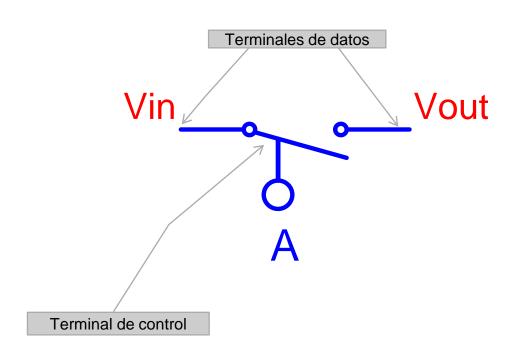

### **EL INTERRUPTOR IDEAL**

- Un interruptor ideal es un dispositivo de tres terminales usado para controlar la conexión eléctrica entre dos puntos de un circuito

- ■Un interruptor ideal crearía un cortocircuito cuando está cerrado y un circuito abierto cuando está abierto, de manera similar a un interruptor mecánico.

| А | Vout   |

|---|--------|

| 0 | Alta Z |

| 1 | Vin    |

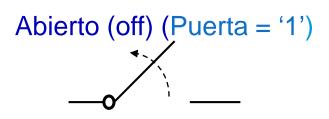

## MODELO DE INTERRUPTOR nMOS

■Suponiendo que los terminales de drenador y fuente son idénticos, la entrada (podría ser analógica) estaría conectada al terminal de drenador y la señal de control al terminal de puerta como se muestra.

Abierto (off) (Puerta = '0')

$$|V_{GS}| < |V_{th}|$$

Cerrado (on) (puerta = '1')

R<sub>on</sub>

$$|V_{GS}| > |V_{th}|$$

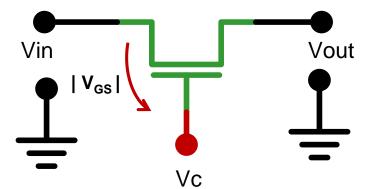

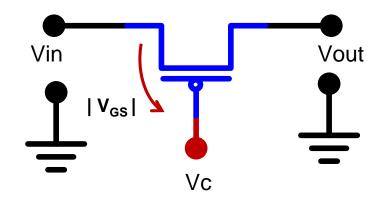

# Modelo de interruptor pMOS

- El transistor pMOS es similar pero opuesto en polaridad al dispositivo nMOS anterior con la corriente que fluye en la dirección opuesta, desde la fuente hasta el drenador. Luego, para un dispositivo pMOS, la entrada se conecta al terminal Fuente y la señal de control al terminal de puerta como se muestra..

- ■Para el pMOS FET, cuando la tensión de control, V<sub>C</sub> en la puerta es cero y, por lo tanto, es más negativa con respecto al terminal de entrada (fuente) o al terminal de salida (drenaje), el transistor está "ON" y en su región de saturación actuando como un interruptor cerrado.

$$|V_{GS}| < |V_{th}|$$

Cerrado (on) (puerta = '0')

$$- V_{GS} > |V_{th}|$$

TC.Tema 4 Pg 5

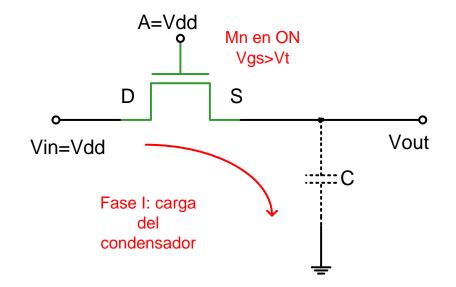

# LIMITACIONES DE LOS INTERRUPTORES nMOS Y pMOS FASE DE CARGA

Una de las limitaciones mas importantes del interruptor nMOS es que transmite de forma degradada el valor "1", como se muestra a continuación, debido a la capacidad parásita de salida

Cuando tras transmitir un "0", sobreviene un nivel alto Vdd ("1"), en esta situación, el condensador comienza a cargarse y al alcanzar la tensión Vdd-Vt el MOS se corta

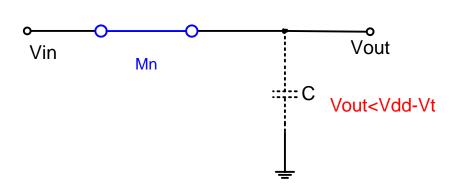

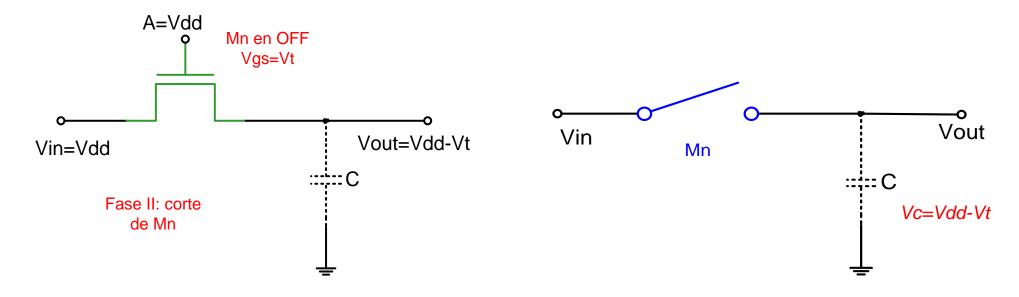

# LIMITACIONES DE LOS INTERRUPTORES nMOS Y pMOS FASE DE CORTE

Cuando el condensador adquiere la tensión Vdd-Vt tendremos que... Vgs=Vdd-(Vdd-Vt)=Vt

A partir de este momento el MOS de corta, el condensador deja de cargarse y la tensión de salida queda fijada a Vdd-Vt.

- La lógica de interruptores se basa en los transistores de paso

- Se pueden implementar funciones lógicas básicas y avanzadas usando las capacidades del MOS como interruptor

- Las implementaciones resultantes tienen las ventajas de ser **simples** (número mínimo de transistores) y rápidas (bajas capacidades parásitas)

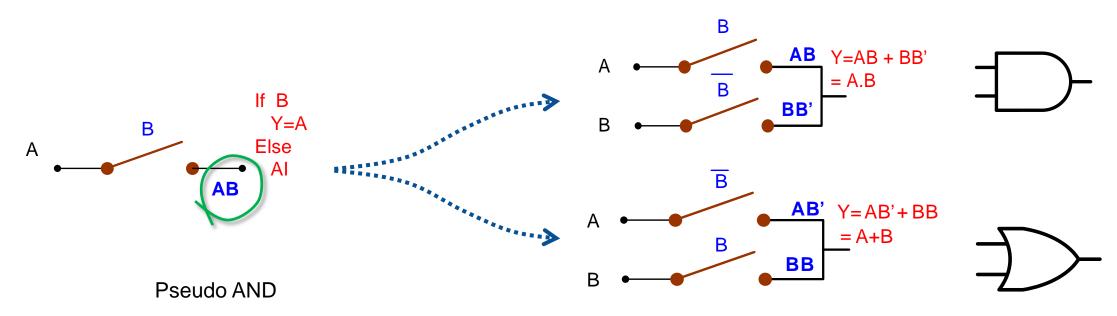

# PSEUDO-IMPLEMENTACIÓN DE FUNCIONES BOOLEANAS MEDIANTE INTERRUPTORES

- Las estructuras de las figuras muestran una lógica *pseudo-or* y *pseudo-and*, esto es, estructuras "or y and" sin terminar.

- ■Nótese que si no se cumple la condición "si" tendremos como resultado alta impedancia. Si X=1 en el primer circuito tendríamos una AND y en el segundo una OR

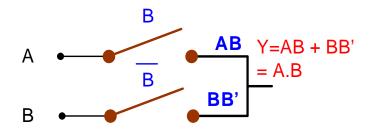

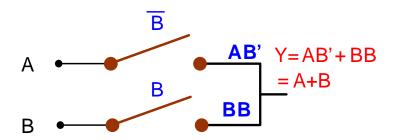

# LÓGICA DE TRANSISTORES DE PASO (PTL)

### PUERTA AND Y OR

- Las puertas AND y OR son estáticas y se implementan con la mitad de transistores que con CMOS

- No hay consumo estático de potencia.

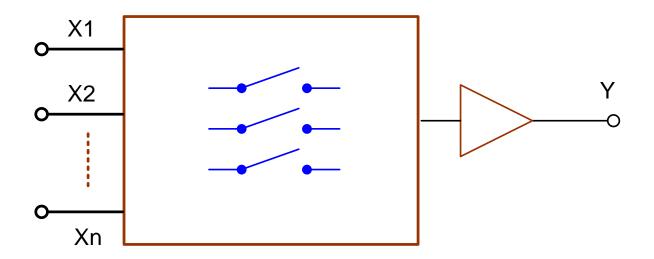

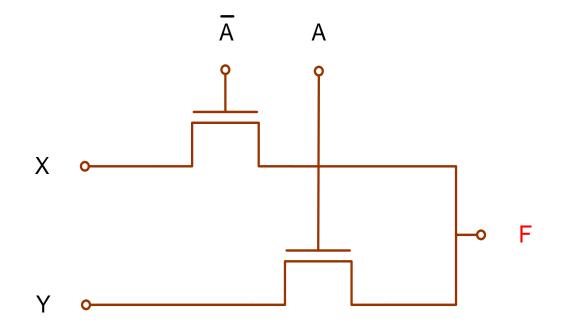

# TOPOLOGÍA GENERAL PTL Y FUNCIONES QUE PUEDE REALIZAR

| Х                | Υ              | F                             |

|------------------|----------------|-------------------------------|

| 0                | 0              | 0                             |

| 0                | 1              | Α                             |

| 1                | 0              | $\overline{A}$                |

| 1                | 1              | 1                             |

| 0                | В              | AB                            |

| 0                | $\overline{B}$ | $A\overline{B}$               |

| 1                | $\overline{B}$ | $\overline{A} + B$            |

| 1                | <u>B</u>       | $\overline{A} + \overline{B}$ |

| В                | 0              | $\overline{A}B$               |

| $\overline{B}$ B | В              | $\overline{A \oplus B}$       |

| В                | $\overline{B}$ | $A \oplus B$                  |

| В                | В              | В                             |

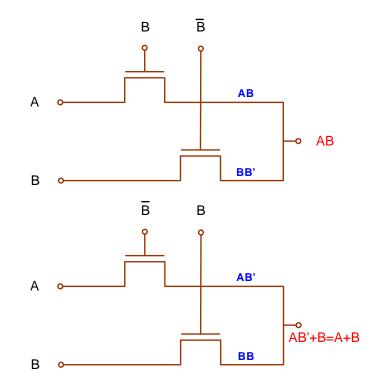

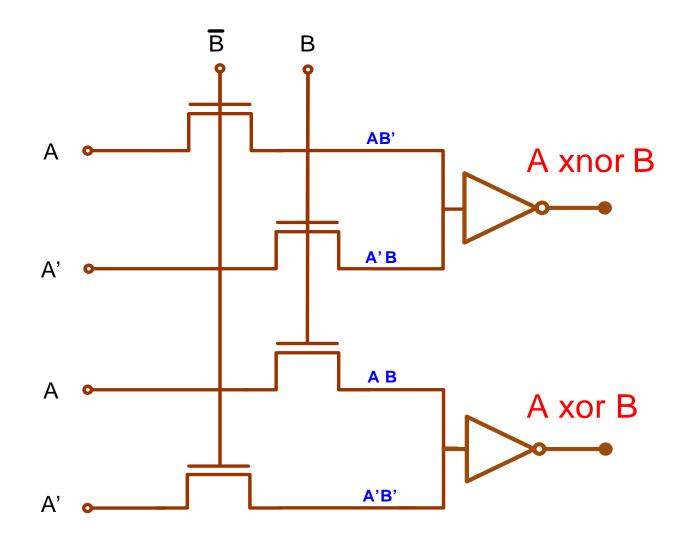

# LÓGICA DE TRANSISTORES DE PASO COMPLEMENTARIA (CPL)

COMPLEMENTARY PASS-TRANSISTOR LOGIC (I)

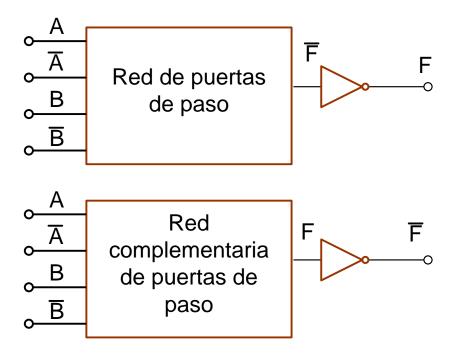

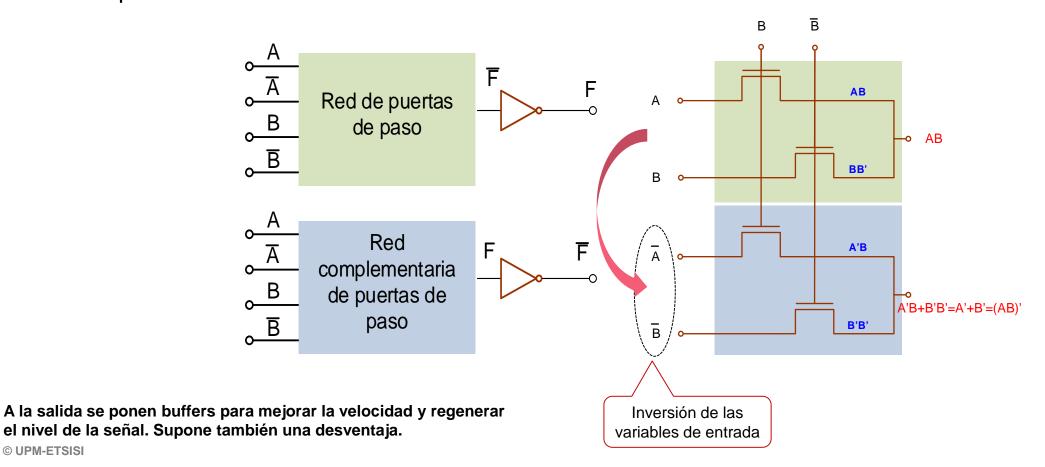

- La lógica de transistores de paso complementaria ó CPL es una lógica diferencial puesto que implementa dos caminos de datos complementarios

- ■Optimiza el número de transistores, elimina el inversor de salida, es muy modular y adecuado para lógica compleja

# LÓGICA DE TRANSISTORES DE PASO COMPLEMENTARIA (CPL)

COMPLEMENTARIEDAD (II)

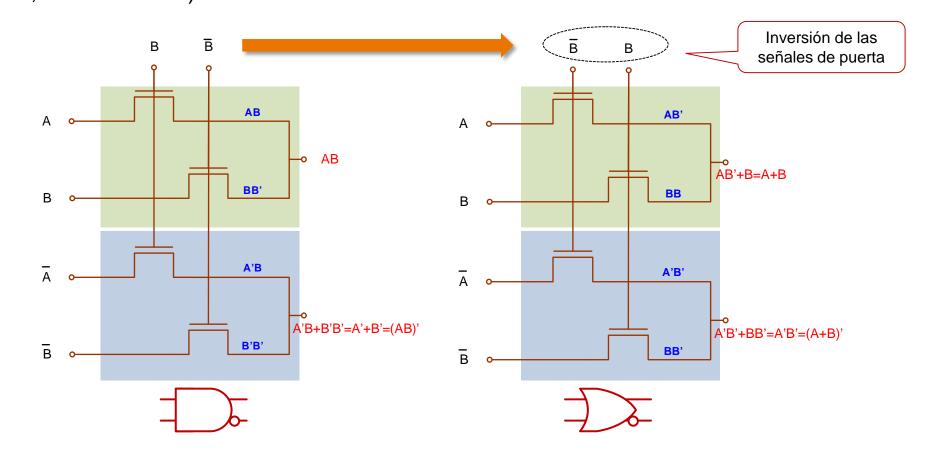

Principio de la complementariedad: Usando la misma topología de circuito que implementa la función "F", con las señales de entrada invertidas (complementarias) la función lógica implementada es F'.

© UPM-ETSISI

# LÓGICA DE TRANSISTORES DE PASO COMPLEMENTARIA (CPL) DUALIDAD (III)

Principio de dualidad: Usando la misma topología de circuito que implementa la función F (pe. AND, NAND, XOR), con las señales de puerta invertidas se obtiene la función dual de F (OR, NOR. XNOR).

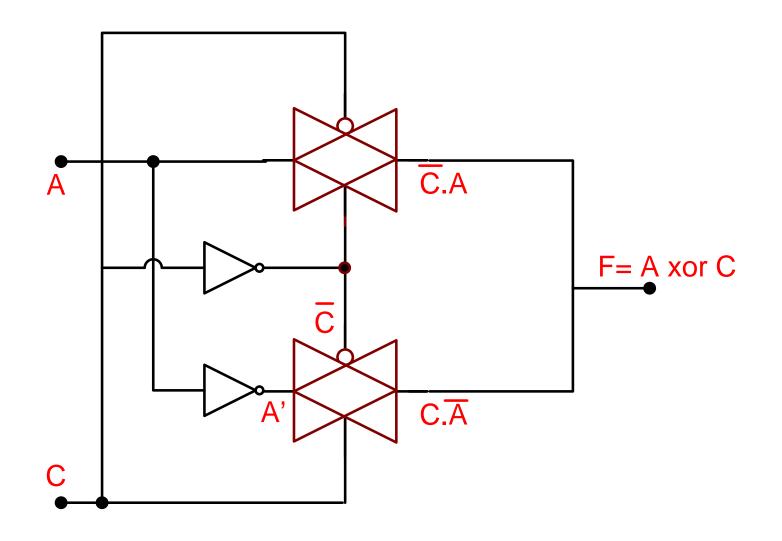

# LÓGICA DE TRANSISTORES DE PASO COMPLEMENTARIA (CPL) PUERTA XOR

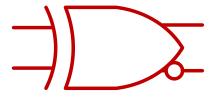

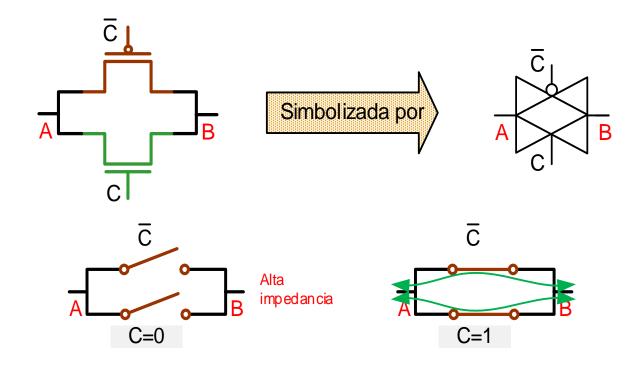

## PUERTA DE TRANSMISIÓN CONCEPTO

- Todo interruptor electrónico *bidireccional* que se cierra o abre controlado por una señal externa recibe el nombre genérico de puerta de transmisión (\*).

- ■Es un interruptor basado en CMOS, en el que los datos se transmiten sin degradación

# IMPLEMENTACIÓN DE LA FUNCIÓN XOR CON PT CMOS

## PUERTA DE TRANSMISIÓN

VENTAJAS E INCONVENIENTES

Aunque la PT se utiliza en innumerables aplicaciones tiene algunos inconvenientes